描述

产品定位与功能

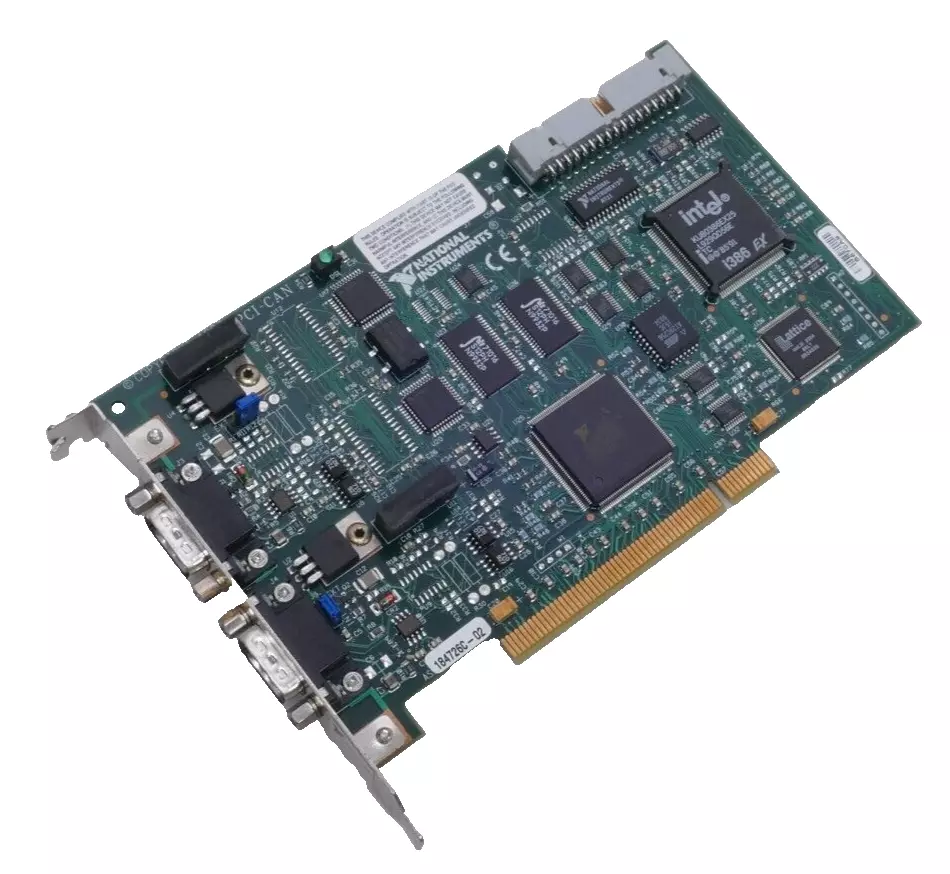

184726c-02推测为NI推出的高密度数字信号处理模块,专为半导体测试、高速通信协议分析及自动化测试系统设计。其核心功能可能包括:

高速数字信号采集与生成:支持多协议(如SPI、I²C)解码与触发;

混合信号处理:集成模拟前端(AFE)实现数模混合测试;

实时同步:多模块级联时钟同步(±100 ps精度)。

核心参数与性能(推测)

数字I/O(DIO)

-通道数:64通道(可配置为独立DI/DO);

-逻辑电平:3.3 V/5 V CMOS/TTL兼容;

-传输速率:≤200 MHz(单端信号)。

模拟前端(可选模块)

-分辨率:12位/16位可切换;

-带宽:DC–500 MHz(高速数字信号捕获)。

接口与通信

-总线类型:PCI Express x4(Gen3,4 GB/s带宽);

-触发机制:支持Pattern触发、边沿触发及协议触发。

技术特点

高密度集成

-通道密度:单槽位实现64通道DIO(传统模块的2倍密度);

-功耗优化:动态电源管理(空闲时功耗降低至30%)。

协议分析能力

-内置状态机:自动识别USB-UART、CAN FD等协议帧;

-错误注入:模拟通信故障(如CRC错误)。

系统扩展性

-菊花链同步:最多8个模块级联(共享时钟与触发);

-混合机箱兼容:支持PXIe与PCIe工业计算机整合。

Product Positioning and Functions

184726c-02 It is speculated that it is a high-density digital signal processing module launched by NI,designed for semiconductor testing,high-speed communication protocol analysis and automated testing systems.Its core functions may include:

High-speed digital signal acquisition and generation:supports multi-protocol(such as SPI,I²C)decoding and triggering;

Mixed signal processing:Integrated analog front-end(AFE)to achieve digital-to-analog hybrid testing;

Real-time synchronization:Multi-module cascade clock synchronization(±100 ps accuracy).

Core parameters and performance(speculation)

Digital I/O(DIO)

-Number of channels:64 channels(configurable as standalone DI/DO);

-Logic level:3.3 V/5 V CMOS/TTL compatible;

-Transmission rate:≤200 MHz(single-ended signal).

Simulate front-end(optional module)

-Resolution:12-bit/16-bit switchable;

-Bandwidth:DC–500 MHz(high-speed digital signal capture).

Interface and communication

-Bus type:PCI Express x4(Gen3,4 GB/s bandwidth);

-Triggering mechanism:Supports Pattern trigger,edge trigger and protocol trigger.

Technical Features

High-density integration

-Channel density:A single slot realizes 64-channel DIO(2 times the density of traditional modules);

-Power consumption optimization:Dynamic power management(reduced to 30%when idle).

Protocol analysis capabilities

-Built-in state machine:automatically recognizes protocol frames such as USB-UART,CAN FD,etc.;

-Error injection:Analog communication failure(such as CRC error).

System scalability

-Daisy chain synchronization:up to 8 modules cascade(shared clock and trigger);

-Hybrid chassis compatibility:supports integration of PXIe and PCIe industrial computers.