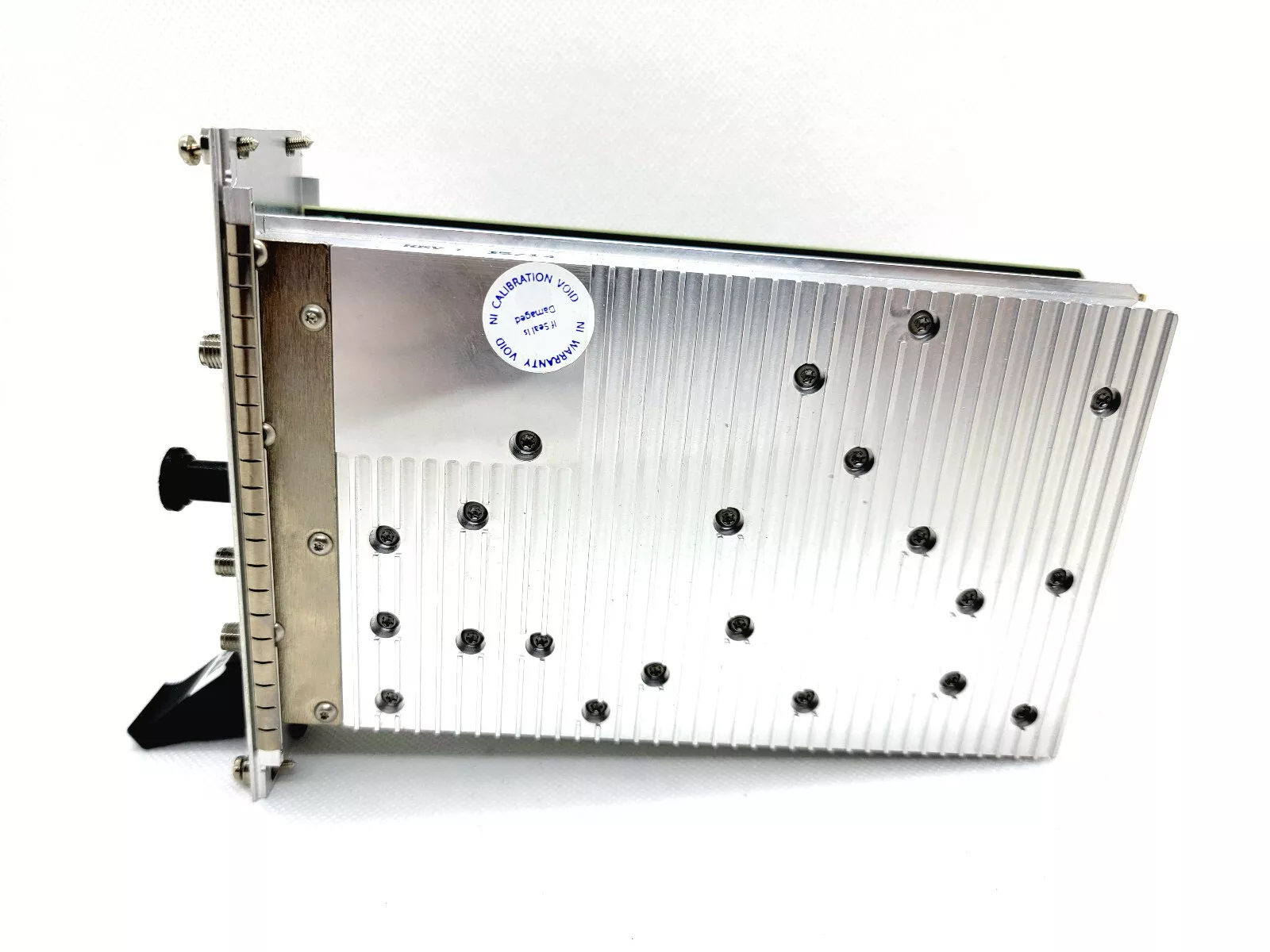

描述

产品定位与功能

NI PXIe-5653推测为PXI Express平台高带宽数字化仪/波形发生器,专为高速信号采集与生成场景设计,适用于航空航天测试、高速数字通信验证及动态信号分析。其核心功能包括:

多通道同步采样:支持8/16通道同步(可配置);

高采样率:≥1 GS/s(单通道模式);

灵活触发:边沿/脉冲宽度/模式触发(支持复杂事件逻辑)。

核心参数与性能

信号采集链路

-带宽:DC–250 MHz(-3 dB点);

-分辨率:16/14 bit(可选配置);

-动态范围:≥70 dB SINAD(典型值)。

数据传输与存储

-系统带宽:4×PCIe×1链路(理论峰值1.06 GB/s);

-板载缓存:2 GB DDR4(支持波形预加载与后处理)。

物理接口

-信号输入/输出:BNC接头(差分/单端可选);

-同步信号:PXIe Star Trigger及外部参考时钟(10 MHz输入/输出)。

技术特点

架构优化

-FPGA协处理:内置Xilinx Artix-7 FPGA实现高速信号预处理(如FFT实时计算);

-分布式时钟:通过PXIe背板同步多模块相位(抖动<100 fs)。

软件生态

-驱动兼容:NI-DAQmx与LabVIEW信号处理工具包;

-协议支持:JESD204B接口标准(高速ADC/DAC链路)。

环境适应性

-抖动容限:±50 ppm(时钟同步场景需外接OCXO参考源);

-散热设计:被动散热(依赖机箱风扇)。

典型应用场景

高速通信测试

-5G毫米波信号实时捕获(带宽>200 MHz);

-光通信眼图分析(10 Gbps以上速率)。

动态物理量测量

-振动台多轴加速度信号同步采集(抗混叠滤波器集成);

-爆炸冲击波压力传感器阵列记录(高g力冲击耐受设计)。

Product Positioning and Functions

NI PXIe-5653 is speculated to be a high-bandwidth digitizer/waveform generator for PXI Express platform,designed for high-speed signal acquisition and generation scenarios,suitable for aerospace testing,high-speed digital communication verification and dynamic signal analysis.Its core functions include:

Multi-channel synchronous sampling:supports 8/16 channel synchronization(configurable);

High sampling rate:≥1 GS/s(single channel mode);

Flexible trigger:Edge/Pulse Width/Mode Trigger(supports complex event logic).

Core parameters and performance

Signal acquisition link

-Bandwidth:DC–250 MHz(-3 dB points);

-Resolution:16/14 bit(optional configuration);

-Dynamic range:≥70 dB SINAD(typical).

Data transmission and storage

-System bandwidth:4×PCIe×1 link(theoretical peak 1.06 GB/s);

-Onboard cache:2 GB DDR4(supports waveform preloading and post-processing).

Physical interface

-Signal input/output:BNC connector(differential/single-ended optional);

-Synchronous signal:PXIe Star Trigger and external reference clock(10 MHz input/output).

Technical Features

Architecture optimization

-FPGA coprocessing:Built-in Xilinx Artix-7 FPGA realizes high-speed signal preprocessing(such as real-time FFT calculation);

-Distributed Clock:Synchronize multi-module phases through PXIe backplane(jitter<100 fs).

Software Ecology

-Driver compatibility:NI-DAQmx and LabVIEW signal processing toolkit;

-Protocol support:JESD204B interface standard(high-speed ADC/DAC link).

Environmental adaptability

-Jitter tolerance:±50 ppm(clock synchronization scenarios require external OCXO reference source);

-Heat dissipation design:passive heat dissipation(relying on the chassis fan).

Typical application scenarios

High-speed communication test

-Real-time capture of 5G mmWave signal(bandwidth>200 MHz);

-Optical communication eye diagram analysis(rates above 10 Gbps).

Dynamic physical quantity measurement

-Synchronous acquisition of multi-axis acceleration signals of vibration table(anti-aliasing filter integration);

-Explosion shock wave pressure sensor array recording(high g force shock resistance design).